アメリカのメーカー、Bolt Graphics は、Zeus プラットフォームを統合するテストチップのテープアウト段階を完了しました。コンポーネントは大規模な物理的製造段階に進みます。このプロジェクトは主に、ハイパフォーマンス コンピューティングと複雑な人工知能の運用を対象としています。電子ゲームの使用は、同社の戦略計画において二次的な可能性として考えられています。この発表は今週行われ、重労働における高いエネルギー効率の目標を強化するものとなった。

カスタマイズされたアーキテクチャでは、オープン RISC-V 標準に基づくコマンド プロセッサが使用されます。初期設計ではTSMCの12ナノメートル製造プロセスが採用されている。同社は、この分野で伝統的に採用されている GDDR 標準ではなく、LPDDR5X および DDR5 メモリを選択しました。この変更により、生産コストが削減されます。この戦略により、大量のデータを扱う法人顧客向けに、メモリ容量を大幅に増やすことも可能になります。

法人市場やデータセンターに向けた戦略

Zeus プラットフォームは、大企業や研究センターからの特定の要求を満たすことを目指しています。ハイパフォーマンス コンピューティングには、大量の情報を中断することなく同時に処理できる機器が必要です。この提案は、法人部門において NVIDIA と AMD の統合製品に代わる、より経済的な代替手段を確立することを目的としています。現在の市場は、特殊なコンポーネントの不足と主要なソリューションの高価格に悩まされています。新しいアーキテクチャは、この財政的圧力を軽減することを約束します。

テープアウトは、半導体開発における基本的なマイルストーンを表します。このステップは、物理的なファウンドリに出荷する前に論理設計が終了したことを示します。選ばれた顧客は約 4 年間にわたってプラットフォームをテストしてきました。スケーラブルなアーキテクチャにより、さまざまな構成を簡単に作成できます。このシステムは、同じパッケージ内で 1 つ、2 つ、または 4 つのチップレットの統合をサポートします。

エネルギー効率が人工知能の拡大の主なボトルネックになっています。最新のサーバーは膨大な量の電力を消費します。また、複雑で高価な冷却システムも必要です。 Bolt Graphics は、消費ワット当たりの処理量を増やすことで、この方程式を解決しようとしています。データセンターの電気料金の削減は、最適化を求める投資家やテクノロジー大手を惹きつけています。

技術仕様とハードウェアの拡張性

初期ポートフォリオには、さまざまなレベルの要件に適合するオプションが表示されます。モジュールに分割することで、企業は業務に必要な処理能力のみを購入できるようになります。メーカーは、製品ラインの基礎を形成する 3 つの主要な構成について詳しく説明しています。

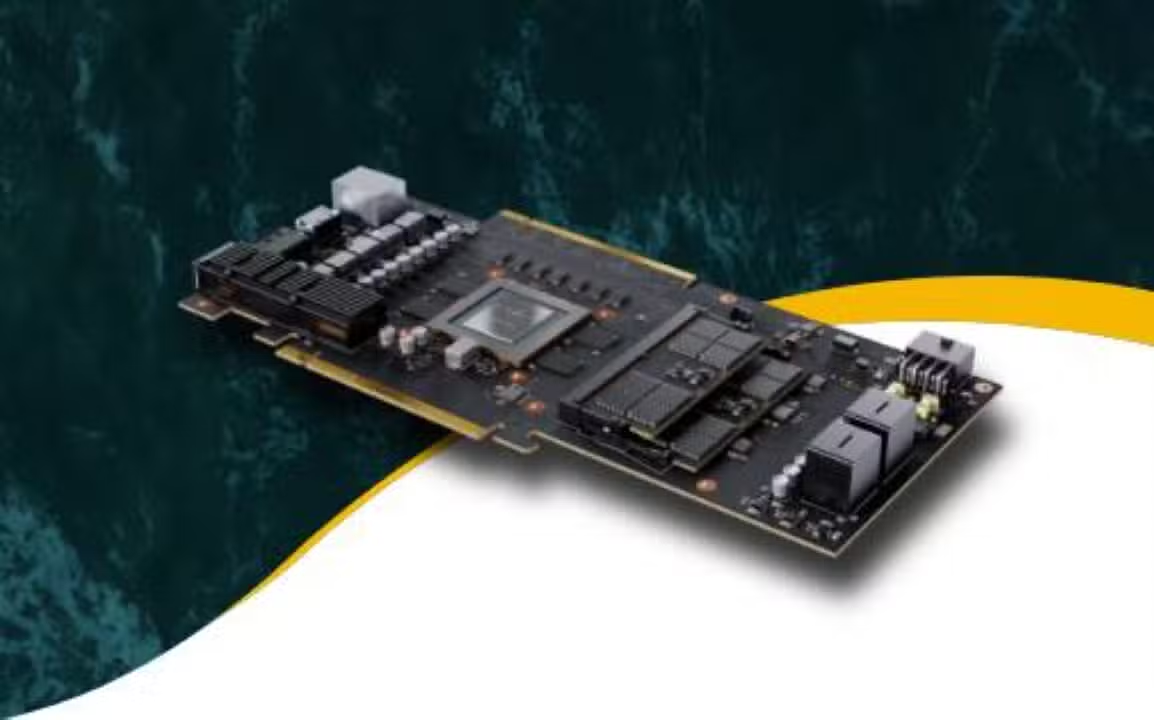

- Bolt Zeus 1c26 モデルは、単一の PCIe スロットを占有し、120 W を消費し、FP16 で 20 TFLOP のパフォーマンスを備えた 32 GB の LPDDR5X メモリを提供します。

- 中間バージョンのBolt Zeus 2c26は、2つのスロットを使用し、250 Wを消費し、256 MBのキャッシュと40 TFLOPに加えて、64 GBまたは128 GBのメモリのオプションを提供します。

- 最上位のBolt Zeus 4c26ボードは消費電力が500 Wに達し、最大256 GBのLPDDR5Xメモリをサポートし、512 MBのキャッシュを備えたFP16で80 TFLOPに達します。

2U フォーマットのサーバー向けのバージョンでは、アーキテクチャの制限が拡張されます。これらのデバイスは、チップに最大 2 GB のキャッシュを統合することを約束します。合計容量は 1TB の LPDDR5X メモリに達します。帯域幅は 5.8 TB/秒に達します。

この仕様では、集中的な並列計算が優先されます。高価なメモリをより手頃な価格の代替品に置き換えることで、総所有コストが削減されます。この戦略は、企業のテクノロジー運用の最も敏感なポイントを直接攻撃します。インフラ予算により、さまざまな機関での研究プロジェクトの拡大が制限されることがよくあります。

シミュレーションにより、高度なレンダリングの利点が示される

メーカーは RTX 5090 グラフィックス カードと直接比較を行いました。 Zeus 2c26 モデルは 250 W で動作します。競合製品の動作には約 575 W が必要です。同社は、そのアーキテクチャが複雑なパス トレース タスクにおいて最大 5 倍優れたパフォーマンスを実現すると主張しています。ハイパフォーマンス コンピューティングのワークロードの増加は 6 倍に達します。

構成がより堅牢になると、内部テストの差が広がります。 4 つのチップレットを搭載したモデルでは、パス トレーシング処理が最大 10 倍高速になることが約束されています。プラットフォーム間の電力消費量に差があるため、数値の妥当性が高まります。このスタートアップは、ラック運用における総所有コストが最大 17 倍削減されると試算しています。このシステムは、直接の競合他社に比べて最大 19 倍のメモリを提供します。

ハードウェアセクターの専門家は、公表されたデータに関して依然として慎重な姿勢を崩さない。この結果は、シリコンの製造前に実行されたシミュレーションから得られます。企業の約束を検証するには、物理ハードウェアでの独立したテストが必要です。メーカー自体は、大規模な商業発売は 2027 年末にのみ行われることを認識しています。

パス トレースへの重点は、専用アクセラレータの使用に基づいています。このアーキテクチャは、従来のビデオ カードに存在する従来のシェーダ モデルを放棄します。この設計では、RISC-V コアと、特に光および物理シミュレーション用に最適化されたブロックが組み合わされています。専門的な作業における高いパフォーマンスは、技術的な選択によって説明されています。同じ設計では、純粋なラスタライズに依存する古いゲームのパフォーマンスが制限される可能性があります。

エコシステムの柔軟性と企業の次のステップ

このプラットフォームは、カスタマイズされたハードウェアと完全なソフトウェア パッケージを統合します。複数の市場との互換性により、さまざまな業界での採用が容易になります。 DDR5 SO-DIMM スロットによるメモリ拡張の可能性は、重要な差別化要因となります。すべての機器を交換せずにサーバーをアップグレードする必要があるシステム管理者にとって、柔軟性は魅力的です。

TSMC での 12 ナノメートル生産に向けた動きは、長年にわたる研究が結実しました。同社はすでに、次世代ではより現代的な製造プロセスに移行することを計画しています。現在のテストチップは、量産前に論理動作を検証するために使用されます。パートナー開発者は、制御された環境でのソリューションの動作をすでに評価しています。

新たな競合他社の出現は世界の半導体市場を動かし、投資家の注目を集めています。特定のニッチ分野に焦点を当てることで、すべてのグラフィックス処理セグメントにおける直接的かつ即時の対立を回避できます。標準化されたコンポーネントの使用により、機械の組み立てが安価になり、長期的なメンテナンスが簡素化されます。テクノロジー部門は、独立した研究所での最初の実用的なテストを待っています。データの確認は、データセンターによる生成人工知能の処理方法を変えることができます。