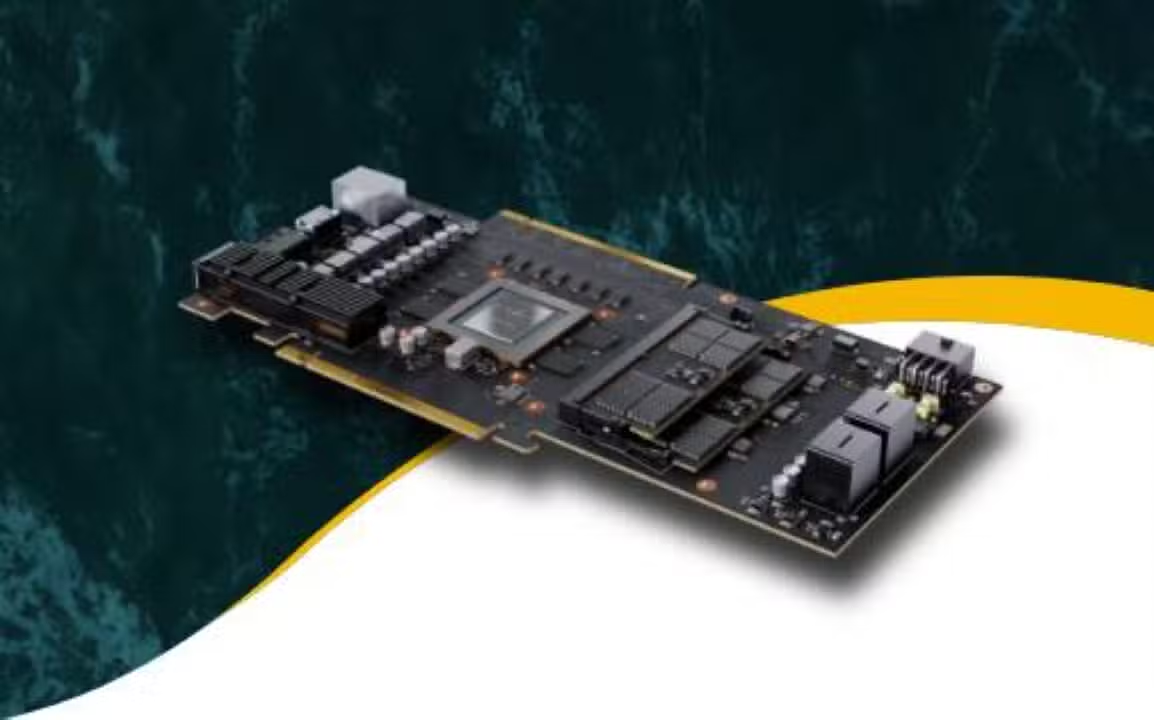

Unprecedented graphics processing architecture advances to testing phase with a focus on artificial intelligence

The American manufacturer Bolt Graphics has completed the tape-out stage of the test chip that integrates the Zeus platform. The component now advances to the large-scale physical manufacturing phase. The project primarily targets high-performance computing and complex artificial intelligence operations. The use of electronic games appears as a secondary possibility in the company’s strategic planning. The announcement took place this week and reinforces the goals of high energy efficiency in heavy tasks.

The customized architecture uses a command processor based on the open RISC-V standard. The initial design adopts TSMC’s 12-nanometer manufacturing process. The company opted for LPDDR5X and DDR5 memories instead of the GDDR standard traditionally found in the sector. The change reduces production costs. The strategy also makes it possible to achieve considerably greater memory capacity for corporate customers who deal with large volumes of data.

Estratégia aimed at the corporate market and data centers

The Zeus platform seeks to meet specific demands from large companies and research centers. High-performance computing requires equipment capable of processing massive volumes of information simultaneously without interruption. The proposal attempts to establish a more economical alternative to consolidated products from NVIDIA and AMD in the corporate segment. The current market suffers from a shortage of specialized components and the high prices of dominant solutions. The new architecture promises to alleviate this financial pressure.

Tape-out represents a fundamental milestone in the development of semiconductors. The step signals the end of logical design before shipping to the physical foundry. Selected Clientes have been testing the platform for around four years. The scalable architecture makes it easy to create varied configurations. The system supports the integration of one, two or four chiplets in the same package.

Energy efficiency has become the main bottleneck for the expansion of artificial intelligence. Modern Servidores consume immense amounts of electricity. Eles also require complex and expensive cooling systems. Bolt Graphics tries to solve this equation by delivering more processing per watt consumed. The reduction in data center electricity bills attracts investors and technology giants looking for optimization.

Especificações technical and hardware scalability

The initial portfolio presents options adapted to different levels of requirement. The division into modules allows companies to purchase only the processing capacity necessary for their operations. The manufacturer has detailed three main configurations that form the basis of the product line.

- The Bolt Zeus 1c26 model occupies a single PCIe slot, consumes 120 W and delivers 32 GB of LPDDR5X memory with 20 TFLOPs performance at FP16.

- The intermediate version Bolt Zeus 2c26 uses two slots and consumes 250 W, offering options of 64 GB or 128 GB of memory, in addition to 256 MB of cache and 40 TFLOPs.

- The high-end Bolt Zeus 4c26 board reaches 500 W consumption, supports up to 256 GB of LPDDR5X memory and reaches 80 TFLOPs in FP16 with 512 MB of cache.

Versions intended for servers in 2U format expand the limits of the architecture. Esses equipment promises up to 2 GB of cache integrated into the chip. The total capacity can reach 1TB of LPDDR5X memory. Bandwidth reaches 5.8 TB/s.

The specifications prioritize intensive parallel computations. Replacing expensive memory with more affordable alternatives lowers the total cost of ownership. The strategy directly attacks the most sensitive point of corporate technology operations. The infrastructure budget often limits the expansion of research projects at different institutions.

Simulações indicate advantages in advanced rendering

The manufacturer made direct comparisons with the RTX 5090 graphics card. The Zeus 2c26 model operates with 250 W. The competitor requires around 575 W to operate. The company claims that its architecture delivers up to five times better performance in complex path tracing tasks. The gain in high-performance computing workloads reaches six times.

The more robust configuration widens the difference in internal tests. The model with four chiplets promises to be up to ten times faster in path tracing processing. The numbers gain relevance due to the gap in electrical consumption between platforms. The startup calculates a reduction of up to seventeen times in the total cost of ownership in rack operations. The system offers up to nineteen times more memory than direct competitors.

Especialistas from the hardware sector remains cautious regarding the released data. The results come from simulations carried out before the silicon was manufactured. Standalone Testes on physical hardware will need to validate the company’s promises. The manufacturer itself recognizes that the large-scale commercial launch will only take place at the end of 2027.

The focus on path tracing is based on the use of dedicated accelerators. The architecture abandons the traditional shader model present in conventional video cards. The design combines RISC-V cores with blocks specifically optimized for light and physics simulations. The technical choice explains the high performance in professional tasks. The same design can limit performance in older games that rely on pure rasterization.

Flexibilidade of the ecosystem and the company’s next steps

The platform integrates customized hardware with a complete software package. Compatibility with multiple markets facilitates adoption by different industries. The possibility of memory expansion through DDR5 SO-DIMM slots represents an important differentiator. Flexibility appeals to system administrators who need to upgrade servers without replacing all the equipment.

The move towards 12 nanometer production at TSMC brings to fruition years of research. The company is already planning to migrate to more modern manufacturing processes in the next generations. The current test chip serves to validate logical operation before mass production. Desenvolvedores partners are already evaluating the solution’s behavior in controlled environments.

The emergence of a new competitor moves the global semiconductor market and attracts the attention of investors. Focusing on specific niches avoids direct and immediate confrontation in all graphics processing segments. The use of standardized components makes machine assembly cheaper and simplifies long-term maintenance. The technology sector awaits the first practical tests in independent laboratories. Data confirmation can transform the way data centers handle generative artificial intelligence.

See Also em Latest News (EN)

Aggressive discount clears PlayStation 5 Pro stocks in the main Brazilian virtual stores

25/04/2026

Targeted action from Microsoft cuts the value of the Xbox Series X in the console store in half

25/04/2026

Resident Evil Village players receive bonuses for movie rentals in the Sony ecosystem

25/04/2026

Valve surprises players and releases four independent titles for free in its digital store

25/04/2026

PlayStation 5 owners gain definitive access to two titles at no extra cost

25/04/2026

Red Dead Redemption 2 update brings 60 FPS and 4K resolution to the new generation of consoles

25/04/2026

Apple prepares iPhone 18 Pro with translucent chassis and 5200 mAh battery for next year

25/04/2026

PlayStation 5 owners receive two major free games on the official store

25/04/2026

Leak details first foldable iPhone with powerful battery and ultra-thin design to outperform rivals

25/04/2026

Nintendo bets on a cheap package with classic Mario game to launch its new console on the market

25/04/2026

Éder Militão will undergo surgery and will be out of the 2026 World Cup

25/04/2026